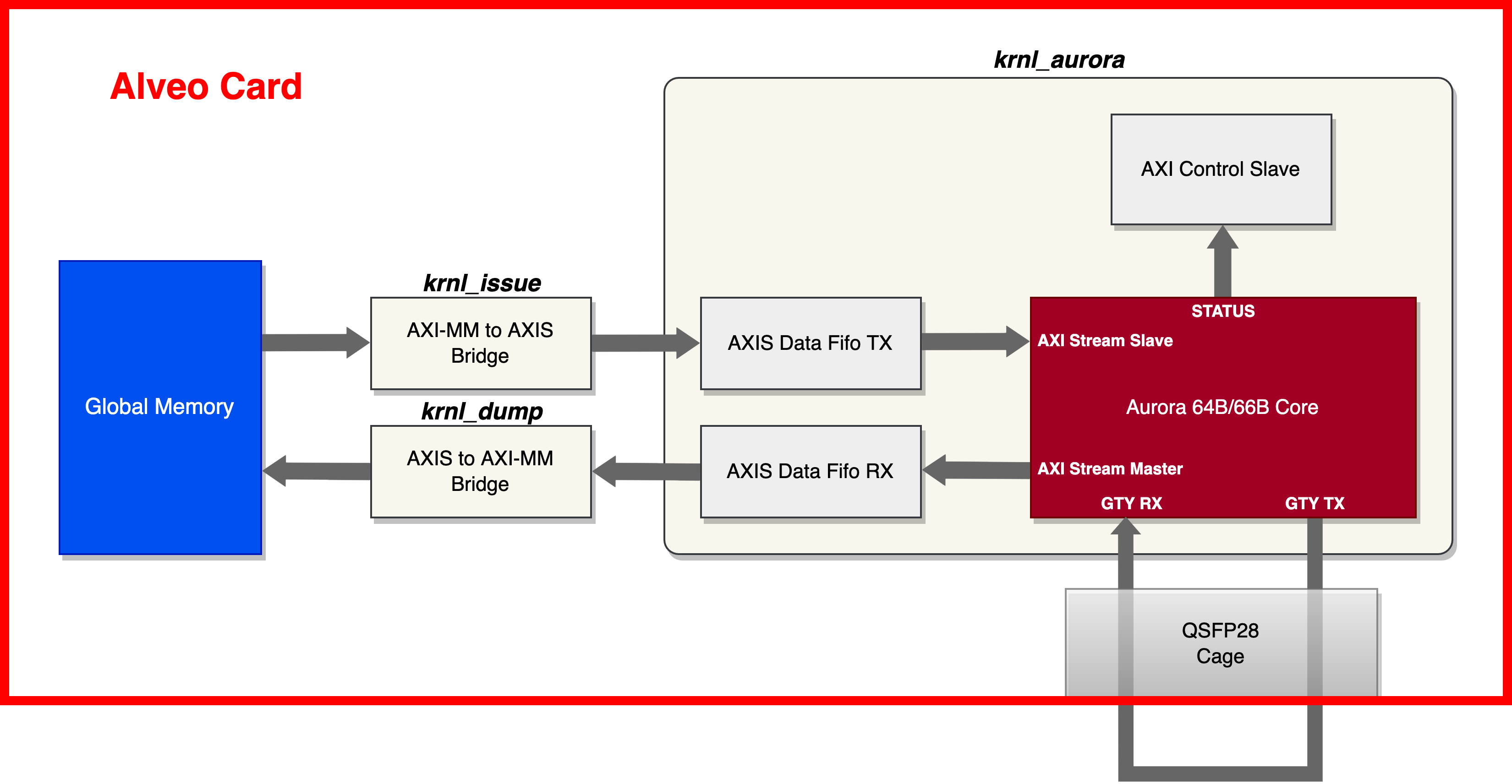

Xilinx Aurora 64b 66b User Guide For details on Aurora 64B 66B IP please refer to Aurora 64B 66B IP Product Guide This tutorial will provide an example design and step by step instruction for integrating Aurora IP into Alveo accelerator cards with Vitis flow The example design integrates a four lane Aurora kernel with 10 Gbps lane rate achieve total 40 Gbps throughput

Dear Xilinx users is there anybody who made already experineces with the AURORA 64B 66B IP Core at a linerate of 25 7813 Gbps on a Kintex Ultrascale device When I calculate the frequency of the user clk which is used for the AXI streaming interface 64bit data width I get a value of around 390MHz This is a very high internal frequency Predefined templates provided for Aurora 8B 10B Aurora 64B 66B CEI 6G DisplayPort Interlaken Open Base Station Architecture Initiative OBSAI OC192 OC48 SRIO 10GBASE R Common Packet Radio Interface CPRI Gigabit Ethernet 10 Gb Attachment Unit Interface XAUI RXAUI and XLAUI OTU3 10GH Small Form factor Pluggable Plus SFP O

Xilinx Aurora 64b 66b User Guide

Xilinx Aurora 64b 66b User Guide

Xilinx Aurora 64b 66b User Guide

https://get.pxhere.com/photo/sky-night-star-atmosphere-night-sky-aurora-113282.jpg

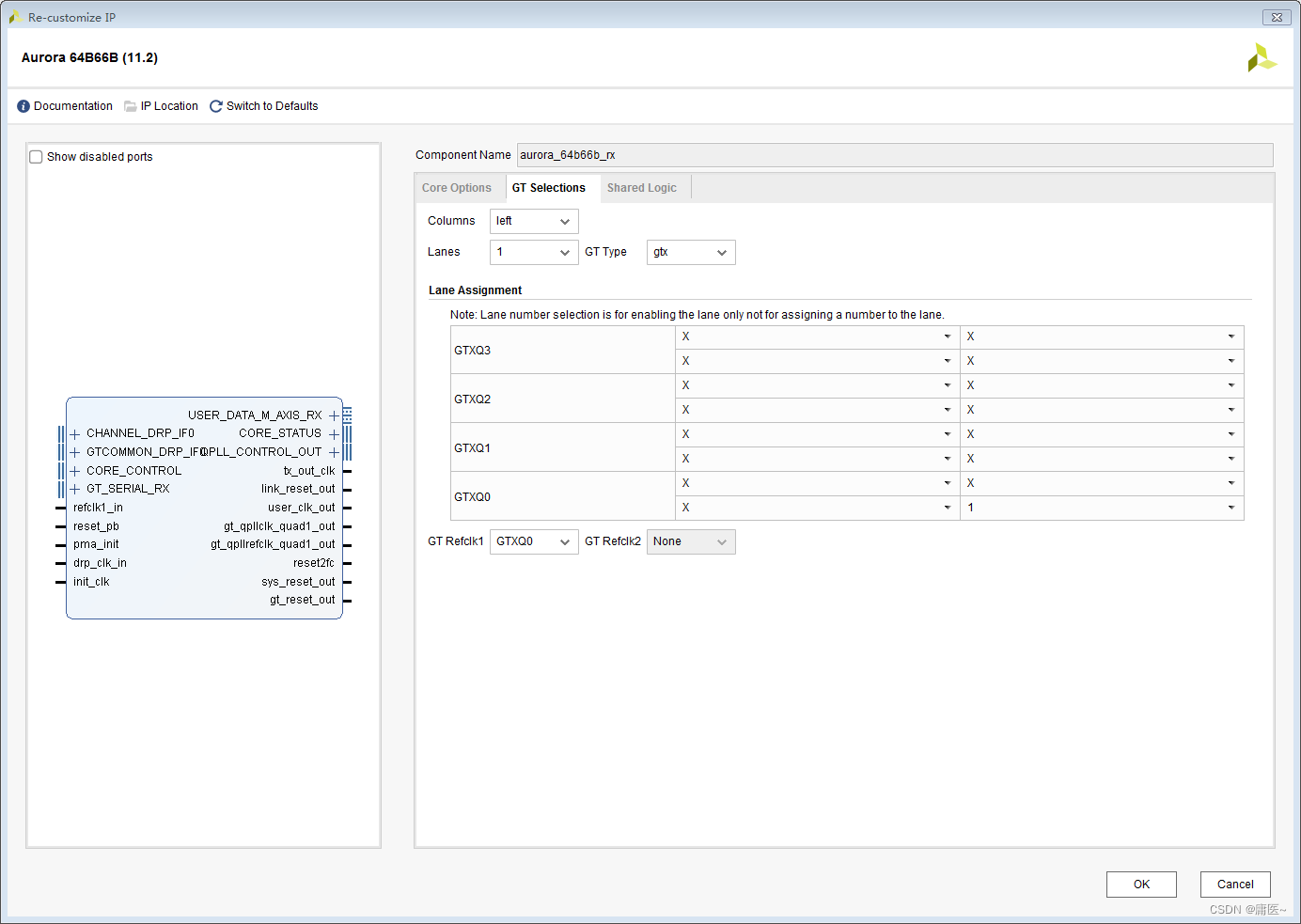

Xilinx recommends migrating the design to Vivado Design Suite and use Aurora 64B66B v9 0 for designs targeting 7 series devices Major changes in Aurora 64B66B v9 0 Aurora 64B66B v9 0 supports only Verilog source code VHDL users can use the netlist only mode through Out Of Context flow

Templates are pre-designed files or files that can be utilized for different functions. They can conserve time and effort by providing a ready-made format and layout for developing different kinds of material. Templates can be utilized for personal or expert jobs, such as resumes, invitations, leaflets, newsletters, reports, presentations, and more.

Xilinx Aurora 64b 66b User Guide

Using Aurora IP In Alveo With Vitis Flow Vitis Tutorials 2022 1

8B 10B 64B 66B

Xilinx Aurora 64B 66B IP

a Aurora 64B 66B based Port b 100 Gigabit Ethernet Port

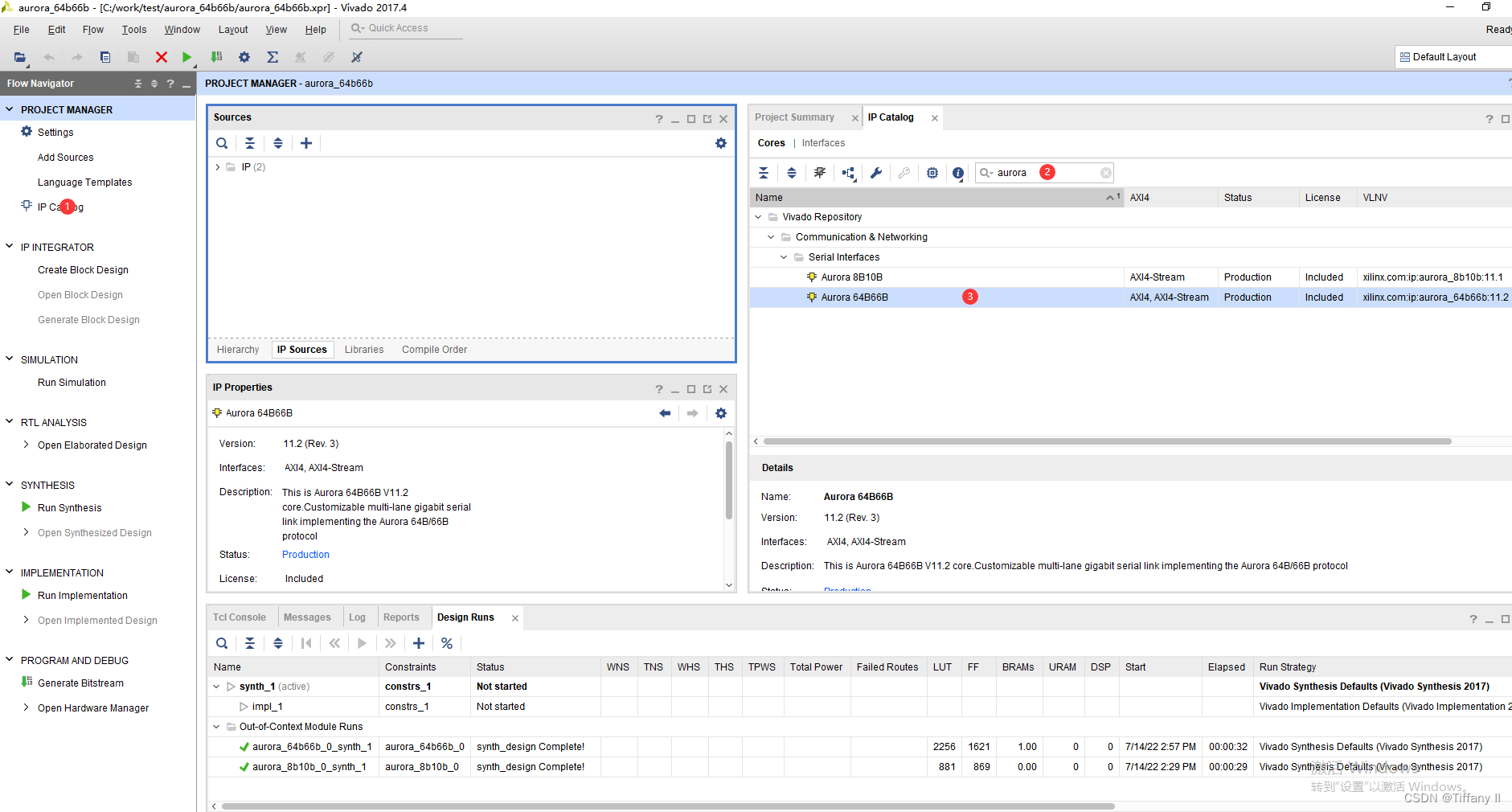

Xilinx Aurora IP aurora CSDN

Aurora 64B 66B CSDN

https://www.xilinx.com/products/intellectual-property/aurora64b66b.html

Streaming data applications Infinite frames with arbitrary Idle insertion make it easy to stream data through Aurora channels Examples Data cell transfer with low overhead Video streams One way connections Aurora simplex channels enable low cost high speed serial links in a single direction

https://docs.xilinx.com/r/en-US/pg074-aurora-64b66b/Aurora-64B/66B-v12.0-LogiCORE-IP-Product-Guide

Documentation Portal Resources Developer Site Xilinx Wiki Xilinx Github Support Support Community

https://support.xilinx.com/s/article/42552?language=en_US

The Xilinx Aurora Solution Center is available to address all questions related to Aurora Solution Known Issues Release Notes URL Name 42552 Article Number 000010222 Publication Date 4 6 2017 IP and Transceivers Other Interface Wireless IP Communication and Networking Aurora 64B 66B Knowledge Base Files 0 Download No records found

https://manualzz.com/doc/11710074/logicore-ip-aurora-64b-66b-user-guide--ug237-

Moved the following sections to the new LogiCORE IP Aurora 64B 66B Getting Started Guide ug238 Aurora 64B 66B Project Directory Structure Example Design Overview FRAME GEN and FRAME CHECK Deleted Using the Build Script section 04 19 10 4 1 LogiCORE IP Aurora 64B 66B v4 1 release Updated core and tools versions

https://japan.xilinx.com/content/dam/xilinx/support/documents/ip_documentation/aurora_64b66b/v4_2/aurora_64b66b_ug237.pdf

All other trademarks are the property of their respective owners Revision History The following table shows the revision history for this document Date Version Revision 03 24 08 1 1 Virtex 5 FPGA Aurora 64B 66B v1 1 release 03 24 08 1 1 1 Miscellaneous typographical edits 06 27 08 1 2 Virtex 5 FPGA Aurora 64B 66B v1 2 release

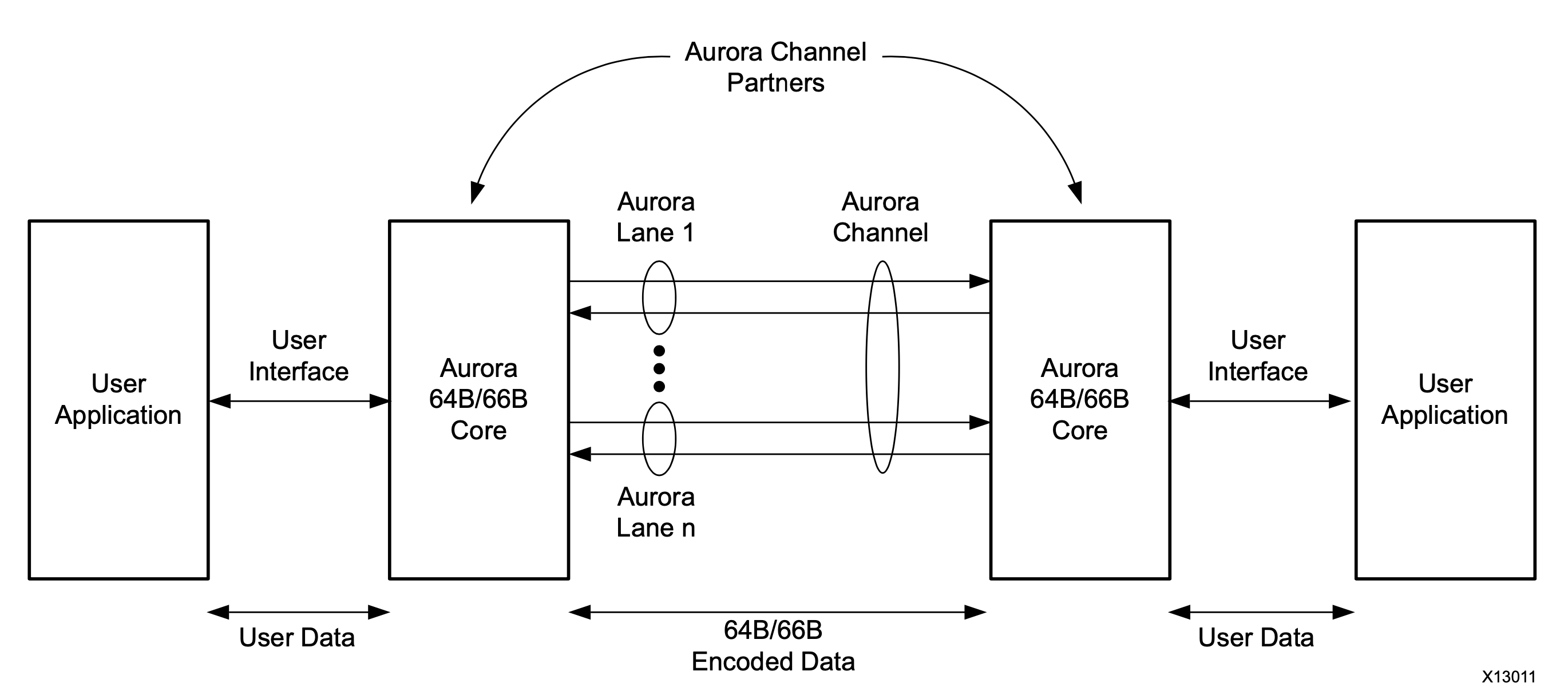

Resource Utilization for Aurora 64B66B v12 0 Vivado Design Suite Release 2019 1 Interpreting the results This page contains resource utilization data for several configurations of this IP core The data is separated into a table per device family In each table each row describes a test case The Aurora Protocol is a link layer communications protocol for use on point to point serial links Developed by Xilinx it is intended for use in high speed gigabits second and more connections internally in a computer or in an embedded system It uses either 8b 10b encoding or 64b 66b encoding The Aurora 8B 10B protocol specification states The Aurora 8B 10B protocol is an open standard

I had worked with aurora core 8b 10b and 64b 66b on zcu102 and be able to transmit data between board to board successfully However this was 4 years ago What I did was straight forward nothing much to change from example design generated by vivado